適配行業(yè)

ACEM是由芯瑞微(上海)電子科技有限公司,基于自主知識(shí)產(chǎn)權(quán)技術(shù)開發(fā)的三維電磁仿真軟件。

作為任意三維結(jié)構(gòu)全波電磁仿真工具,ACEM依托強(qiáng)大的3D編輯、自動(dòng)參數(shù)化和極低的內(nèi)存占用特性,搭載imesh智能加密和網(wǎng)格后處理引擎,高性能的GPU加速,可并行加速的HPC特性,適配于半導(dǎo)體、計(jì)算機(jī)、通信網(wǎng)絡(luò)、車用電子等多個(gè)行業(yè)的設(shè)計(jì)和仿真。

本次案例展現(xiàn)了ACEM對(duì)于DDR5內(nèi)存的優(yōu)化。在云計(jì)算、大數(shù)據(jù)分析、虛擬化等大規(guī)模數(shù)據(jù)中心;人工智能和深度學(xué)習(xí)領(lǐng)域;科學(xué)計(jì)算、工程模擬、氣象預(yù)測(cè)等高性能計(jì)算領(lǐng)域,ACEM都能夠在實(shí)際應(yīng)用層面,提供參考與借鑒。

場(chǎng)景描述

現(xiàn)在電子系統(tǒng)設(shè)計(jì)中,基于DDR5總線技術(shù)的擴(kuò)展應(yīng)用越來(lái)越多,而DDR5總線的最高傳輸速率已經(jīng)達(dá)8.4GT/s。如何保證DDR5總線傳輸?shù)男盘?hào)質(zhì)量,在特定板材下的傳輸距離長(zhǎng)度是多少,等等,都已成為電子系統(tǒng)設(shè)計(jì)必需面對(duì)的設(shè)計(jì)難題。

本案例針對(duì)DDR5總線的高速率、高帶寬、高性能以及點(diǎn)對(duì)點(diǎn)傳輸方式的特點(diǎn),展開了基于POP結(jié)構(gòu)的DDR5鏈路設(shè)計(jì)與信號(hào)完整性(SI)仿真技術(shù)的研究,并結(jié)合上述問(wèn)題對(duì)所設(shè)計(jì)的鏈路進(jìn)行SI仿真,詳細(xì)分析仿真結(jié)果,以此來(lái)研究DDR5的數(shù)據(jù)傳輸速度和吞吐量等信號(hào)完整性問(wèn)題。

案例簡(jiǎn)介

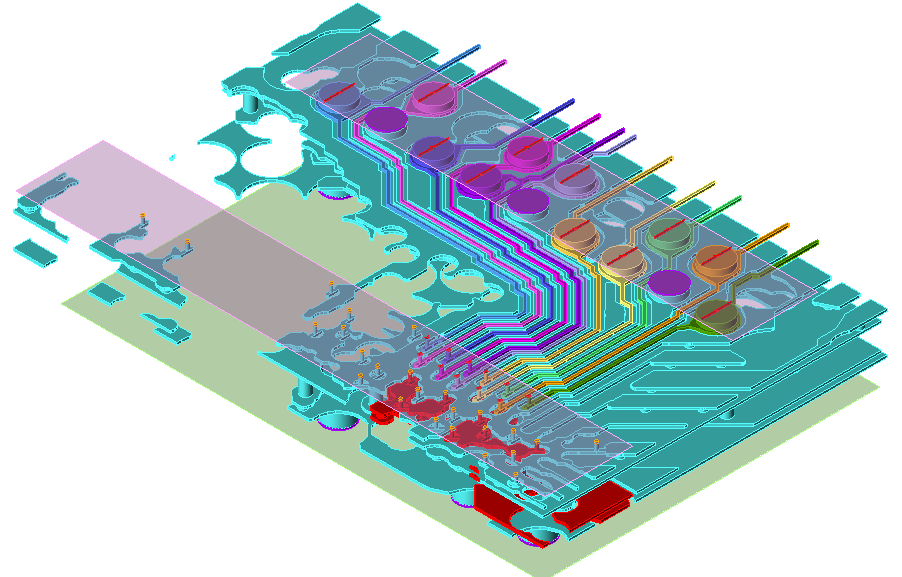

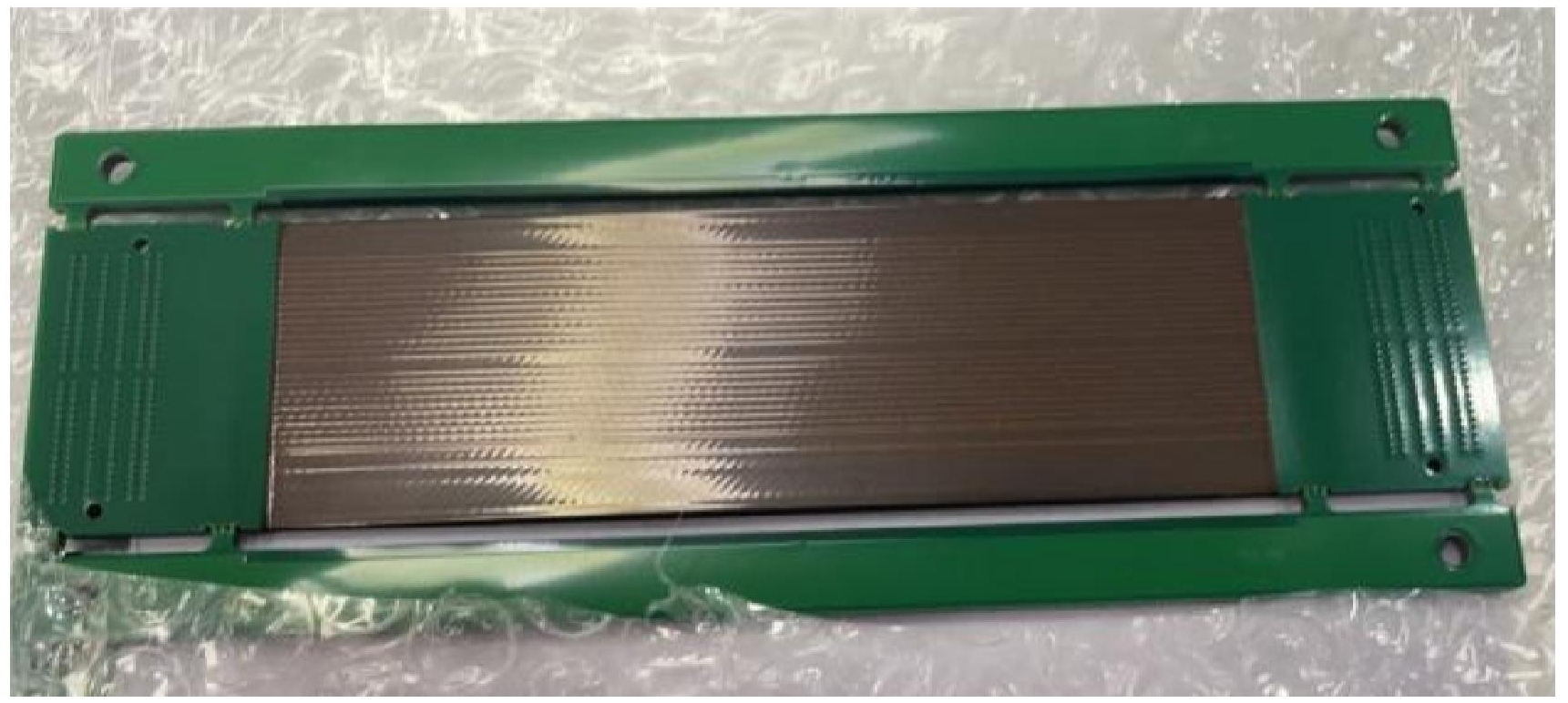

此案例為POP的封裝設(shè)計(jì),用戶通過(guò)ACEM來(lái)優(yōu)化高速并行接口走線設(shè)計(jì),使信道質(zhì)量符合設(shè)計(jì)要求。模型如下圖所示:

仿真設(shè)置

4.1 生成仿真模型,選擇Net和Component設(shè)置

Net Editor 區(qū)域選擇一組DDR信號(hào)進(jìn)行仿真、勾選相關(guān)參考電源、參考地網(wǎng)絡(luò);

Component Editor 區(qū)域設(shè)置焊球、port相關(guān)參數(shù);

在 Information 區(qū)域選擇仿真模式,點(diǎn)擊 Generator cut model 即可生成模型。

4.2 設(shè)置仿真參數(shù)

設(shè)置仿真激勵(lì)、輻射邊界、仿真core,點(diǎn)擊開始就可以運(yùn)行仿真。

仿真效果

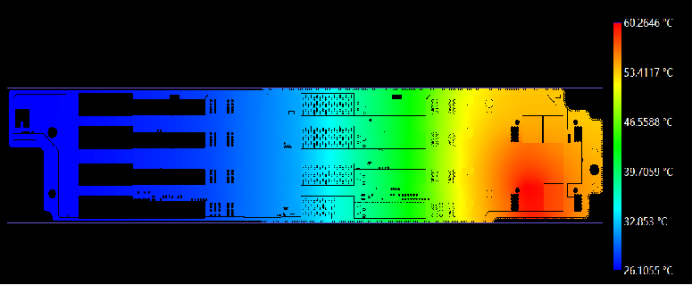

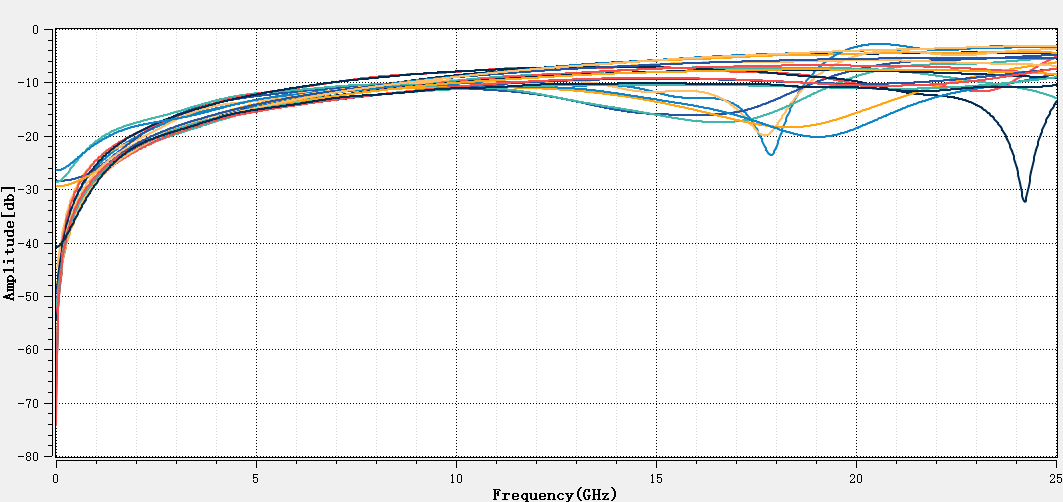

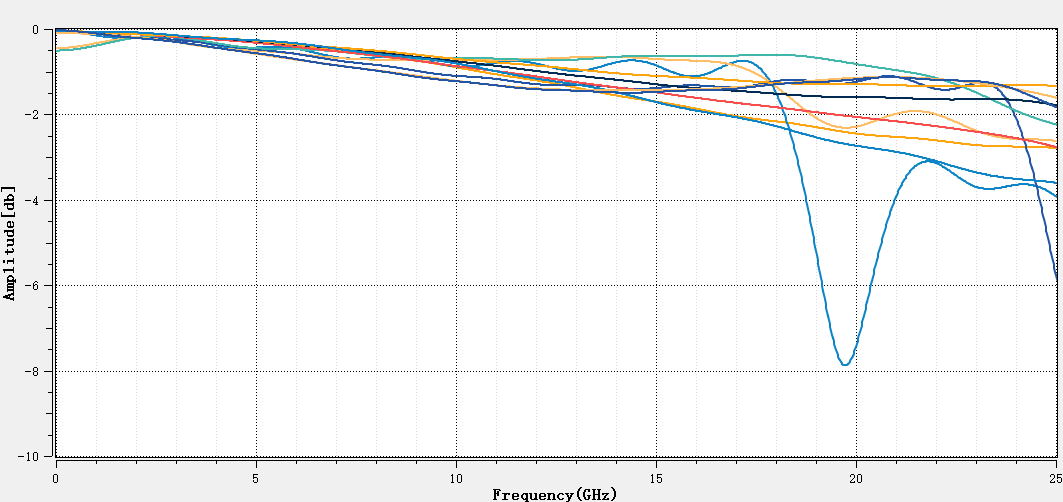

5.1 S參數(shù)分析

回?fù)p: DQ0-DQ7回?fù)p在10G以內(nèi)滿足-10db的要求。

插損:其他端口滿足在-3db以上,DQ0的信號(hào)未滿足要求。

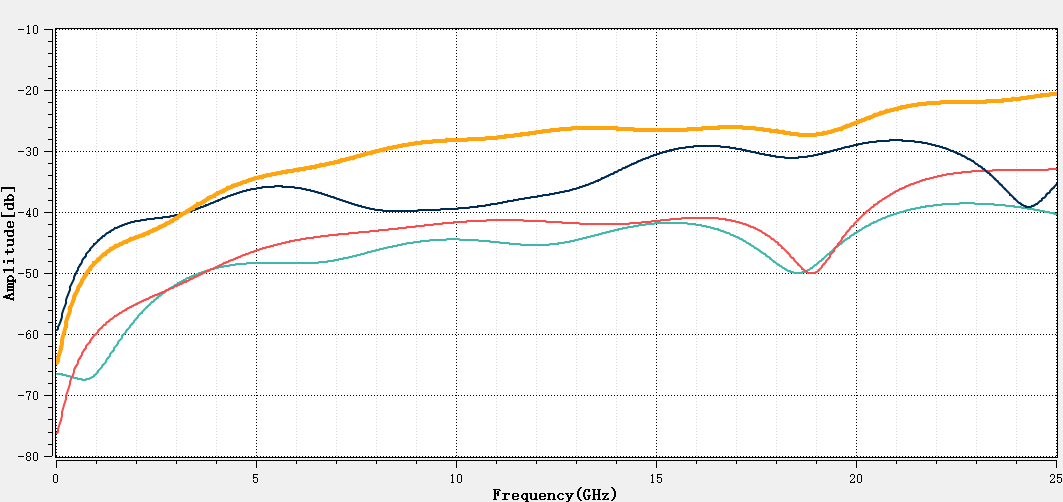

串?dāng)_:其他端口滿足在-30db以下,DQ5的信號(hào)未滿足要求。

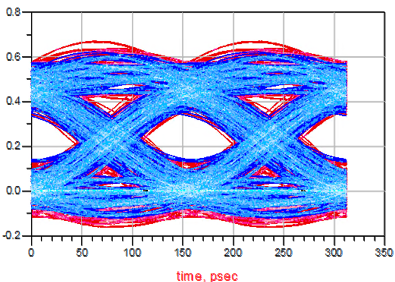

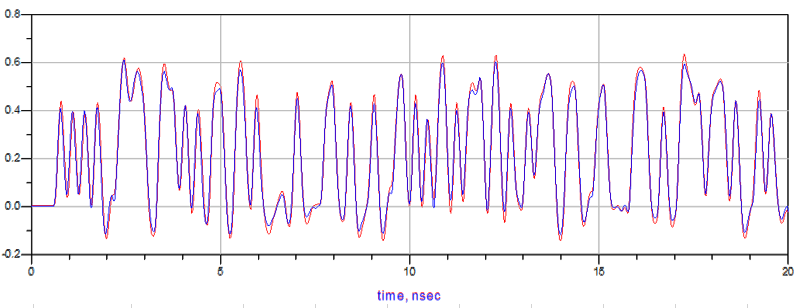

從眼圖可以看出在6400Mbps的眼高為:0.173,眼寬為9.062E-11。

發(fā)現(xiàn)眼睛張開不是很理想,通過(guò)在接收端設(shè)置均衡調(diào)整之后,眼寬和眼高在6400Mbps能夠滿足要求,以及通過(guò)合適的信號(hào)線寬度和阻抗匹配,減少傳輸線的功率衰減和反射。使用終端匹配電阻,降低信號(hào)反射和串?dāng)_的影響。在電路板設(shè)計(jì)中增加地平面和電源層,以提供足夠的屏蔽和隔離,合適地布局阻擋層,減少信號(hào)之間的干擾,優(yōu)化后串?dāng)_滿足相關(guān)技術(shù)性指標(biāo)。

ACEM在此案中的價(jià)值點(diǎn)

在現(xiàn)代計(jì)算系統(tǒng)中,DDR5(第五代雙倍數(shù)據(jù)率)是一種高性能的內(nèi)存標(biāo)準(zhǔn),可以提供更高的數(shù)據(jù)傳輸速度和吞吐量。為了確保DDR5在實(shí)際應(yīng)用中具有穩(wěn)定和可靠的性能,進(jìn)行并行仿真以評(píng)估其信號(hào)完整性是至關(guān)重要的。

本案例通過(guò)ACEM仿真軟件仿真對(duì)DDR5信號(hào)的SI分析,得出最高速率信號(hào)在頻域的spec,提出改善信號(hào)傳輸質(zhì)量、保證信號(hào)完整性的方法, 為實(shí)際應(yīng)用提供了有益參考與借鑒。

仿真場(chǎng)景

本案例是16層PCB電源背板,在載大電流的情況下可能會(huì)出現(xiàn)壓降過(guò)大,導(dǎo)致元器件欠壓或過(guò)孔電流密度較大導(dǎo)致超出過(guò)孔承載裕量等問(wèn)題,嚴(yán)重情況下甚至?xí)龎倪^(guò)孔。通過(guò)PhysimDC仿真分析本案例,驗(yàn)證載240A大電流時(shí)是否出現(xiàn)上述問(wèn)題,載流方案是否可行,大通流的情況下是否帶來(lái)過(guò)大的功耗,過(guò)孔載流是否正常,壓降是否在規(guī)定裕量?jī)?nèi)。

案例簡(jiǎn)介

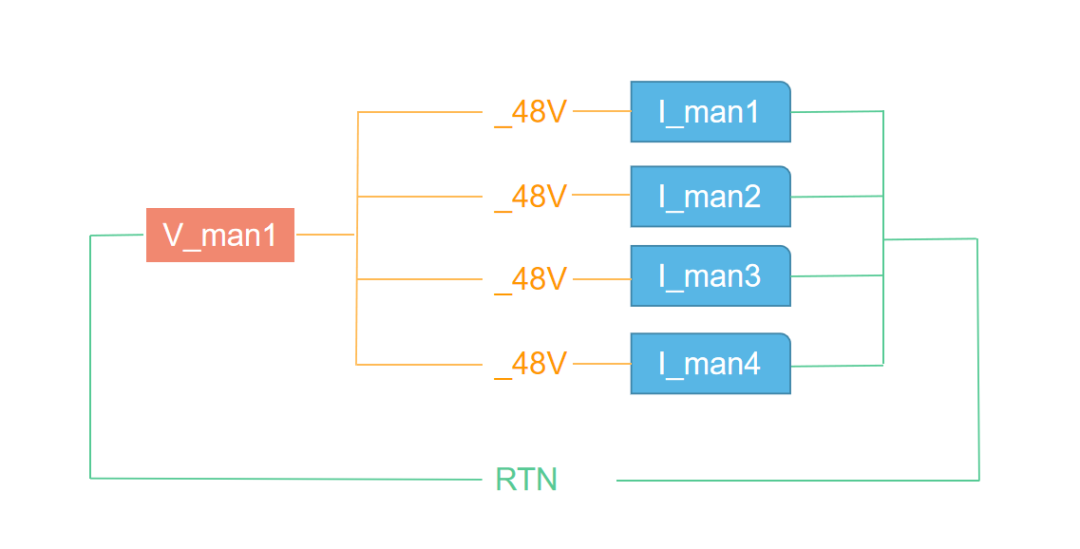

在本案例中,V_source(供電端)為手動(dòng)創(chuàng)建的model——V_man1,加源48V;I_Sink(用電端)為手動(dòng)創(chuàng)建的model——I_man1、I_man2、I_man3以及I_man4,各自載流60A,共240A。

此案例DC仿真的電源網(wǎng)絡(luò)的示意圖如下:

電路連接示意圖

仿真設(shè)置

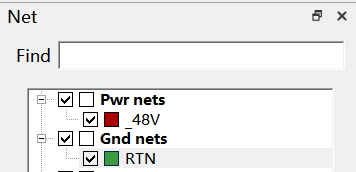

分類電源/地網(wǎng)絡(luò)

將仿真的電源網(wǎng)絡(luò)_48V分類至Pwr Net,將對(duì)應(yīng)的地網(wǎng)絡(luò)分類至Gnd Net。

仿真網(wǎng)絡(luò)分類圖

選擇仿真電模型

本案例沒(méi)有可直接用作DC仿真的元器件,需要用戶手動(dòng)創(chuàng)建Circuit,具體流程操作詳見PhysimDC Tutorial中的案例三。

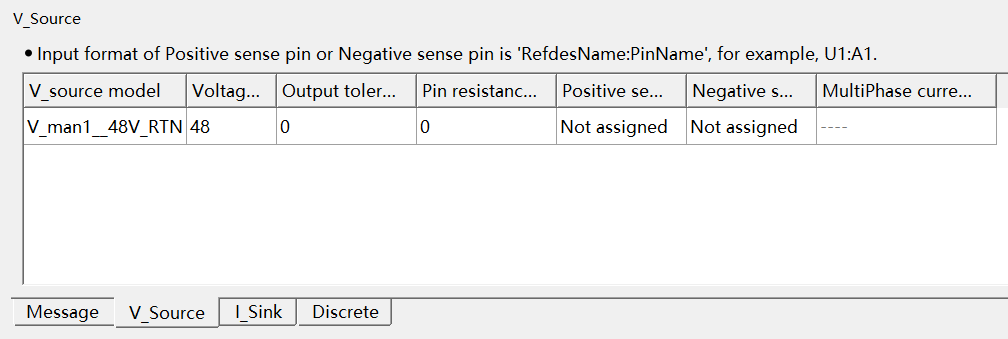

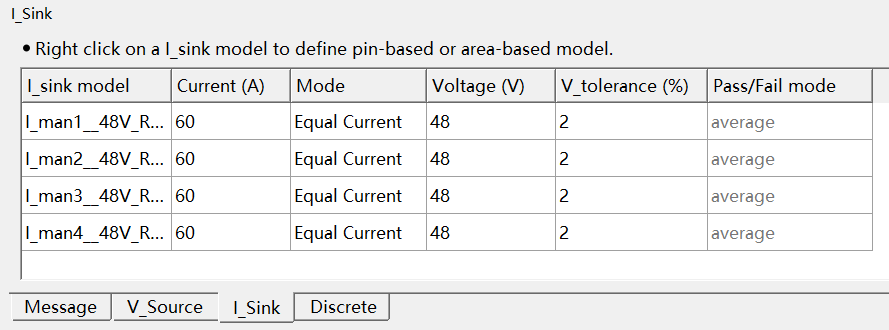

設(shè)置仿真參數(shù)

設(shè)置Vsource加源48V,設(shè)置4個(gè)Isink分別載流60A共240A。

供電端參數(shù)設(shè)置

負(fù)載端參數(shù)設(shè)置

仿真結(jié)果

壓降分析

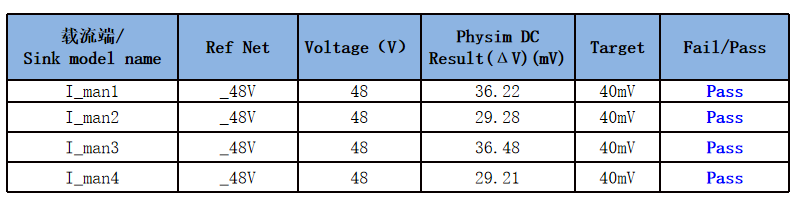

加了240A電流的情況下,仿真壓降在40mV內(nèi),壓降評(píng)估合理。

仿真壓降結(jié)果表格

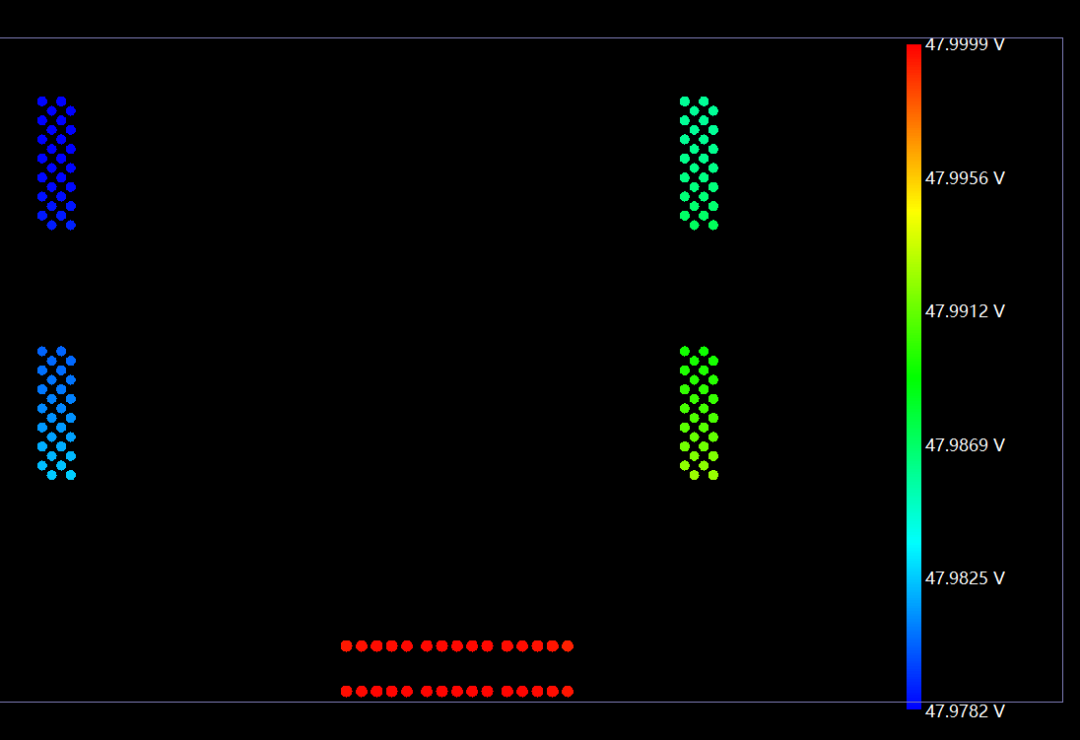

電源網(wǎng)絡(luò)壓降分布云圖1

電源網(wǎng)絡(luò)壓降分布云圖2

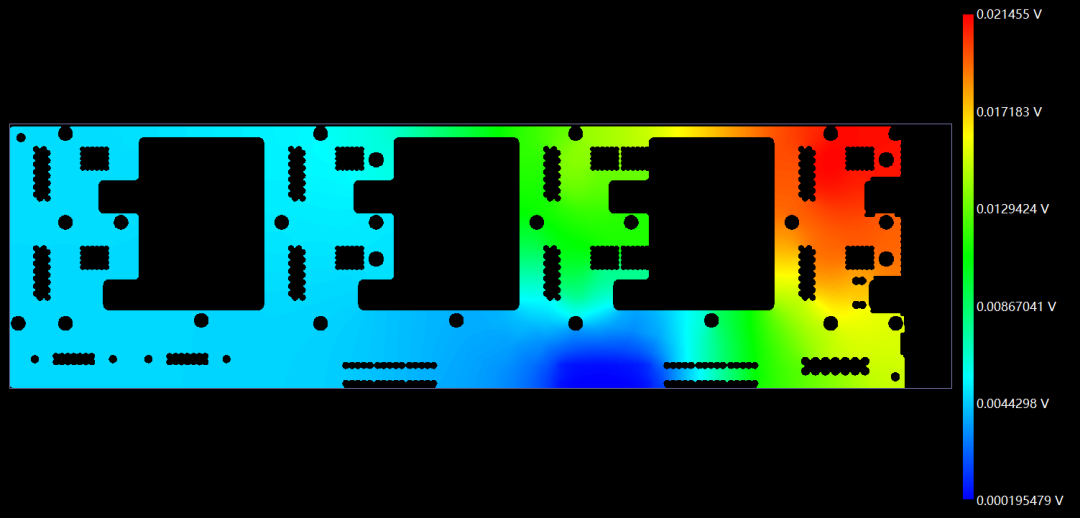

地網(wǎng)絡(luò)壓降分布云圖1

地網(wǎng)絡(luò)壓降分布云圖2

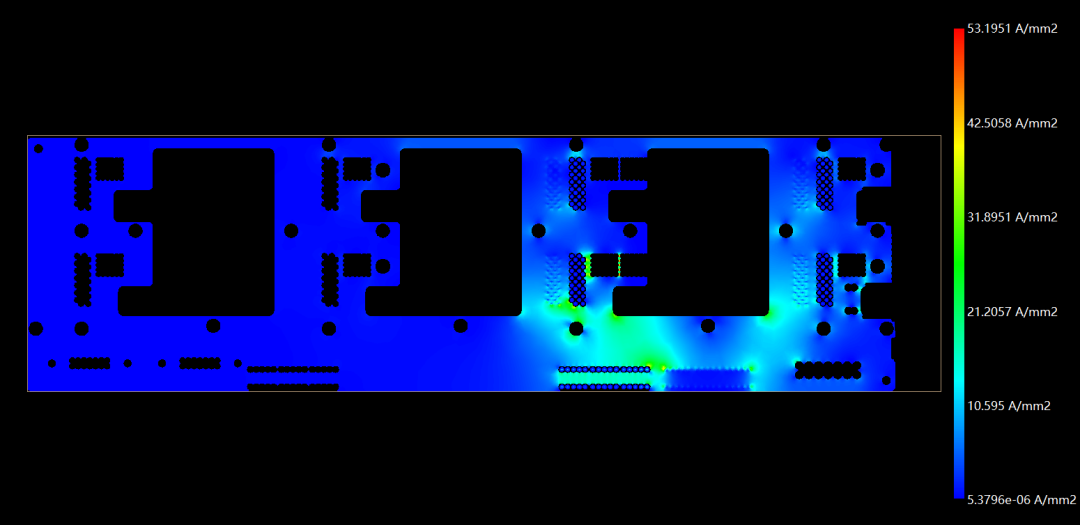

電流密度分析

電流密度分布未出現(xiàn)異常,電流熱點(diǎn)在合理范圍內(nèi),電流密度評(píng)估合理。

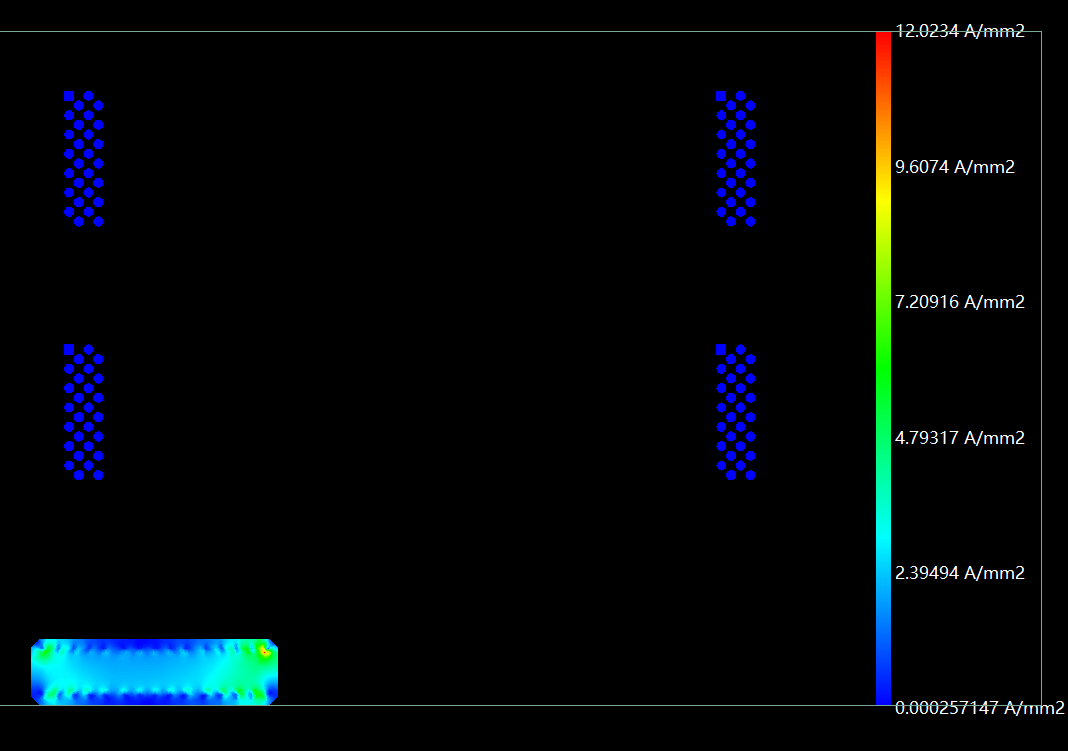

電流密度分布云圖1

電流密度分布云圖2

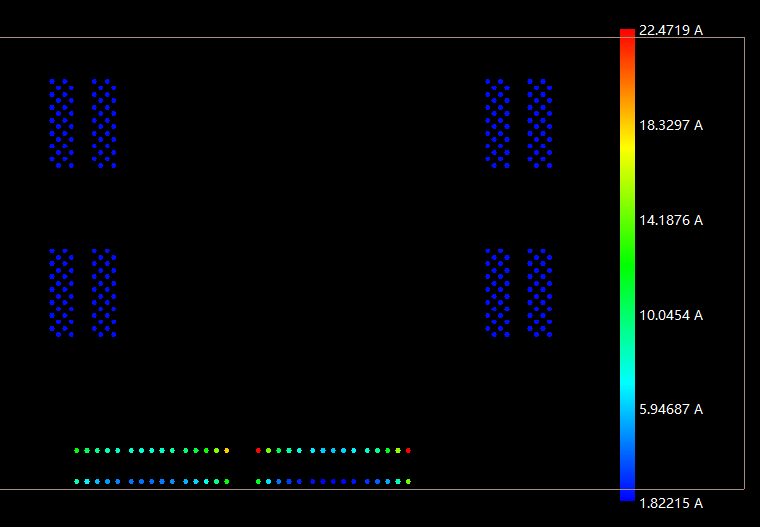

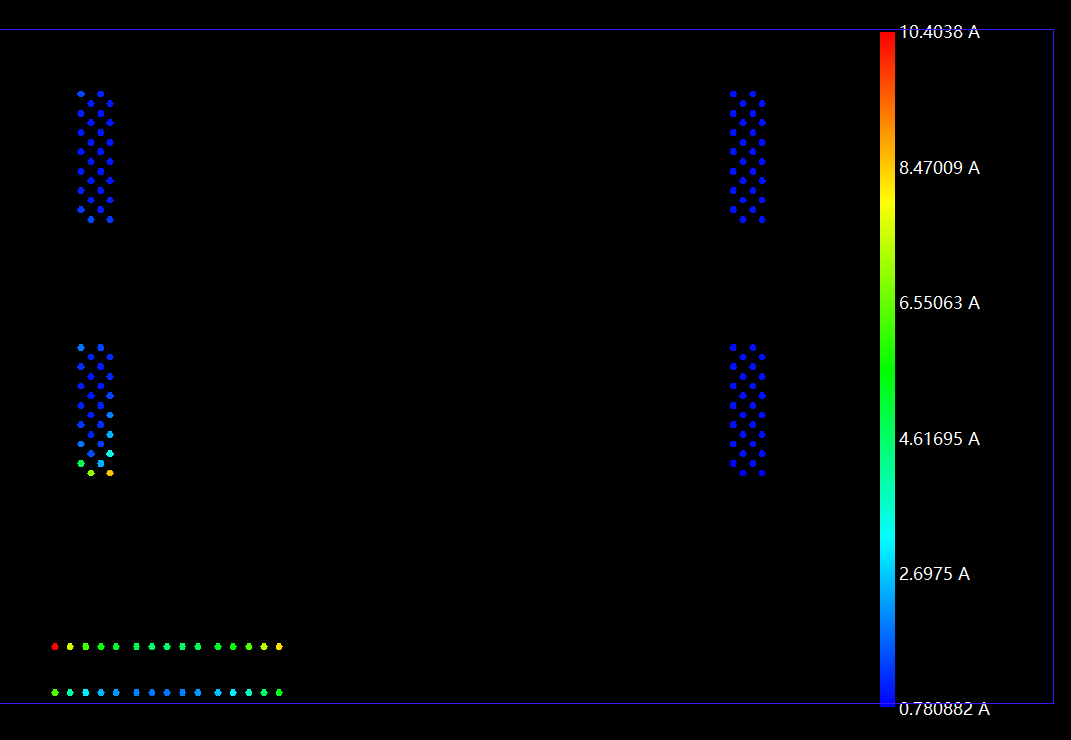

過(guò)孔電流分析

過(guò)孔電流熱點(diǎn)數(shù)據(jù)在過(guò)孔承載的裕量?jī)?nèi),過(guò)孔載流評(píng)估合理。

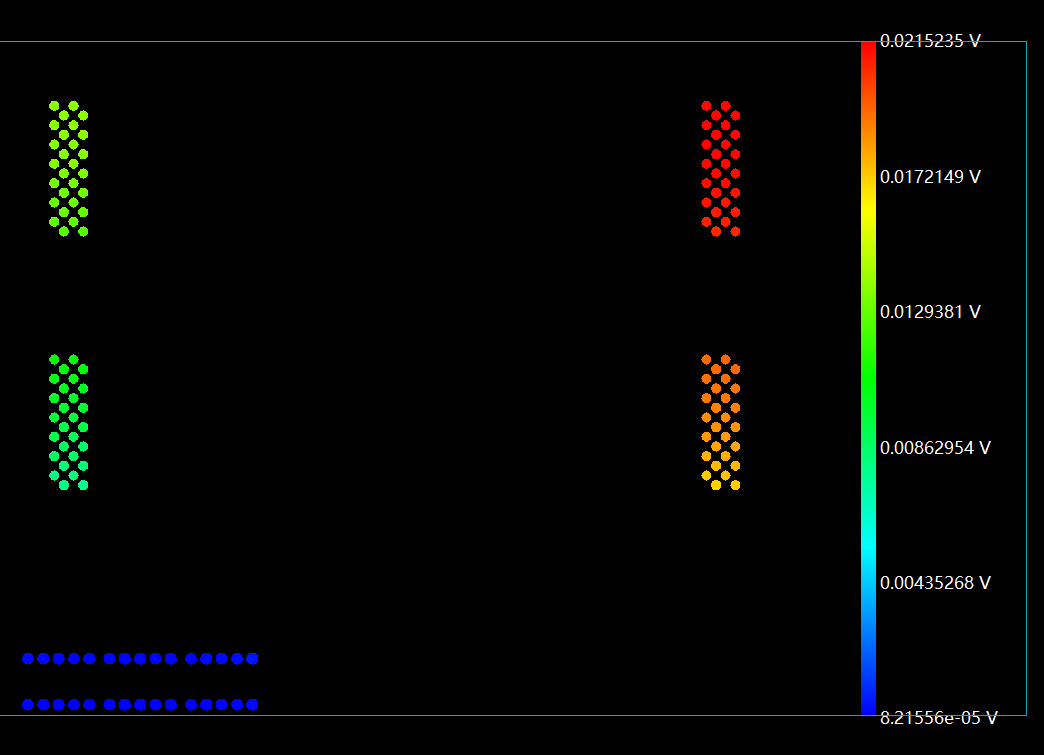

過(guò)孔電流分布云圖1

過(guò)孔電流分布云圖2

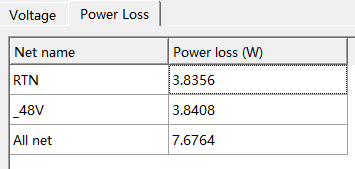

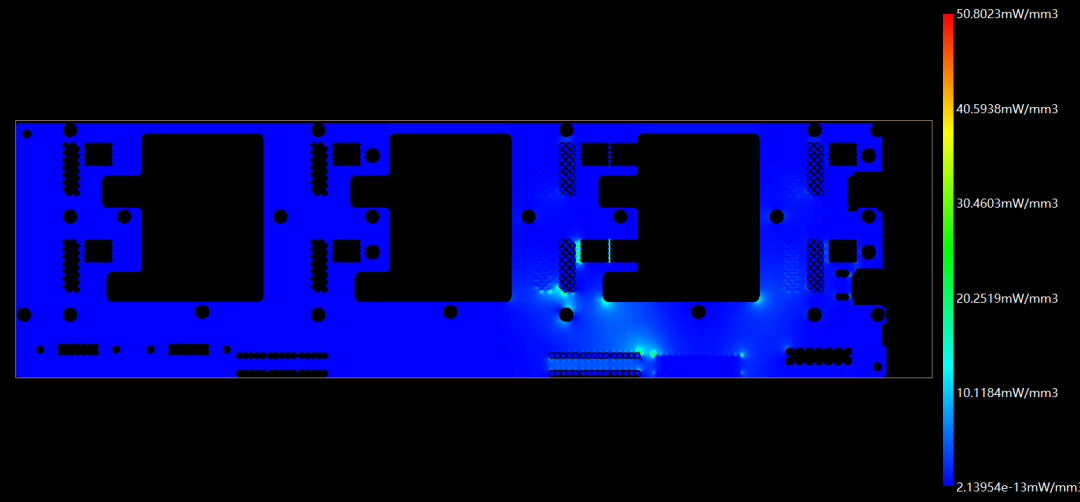

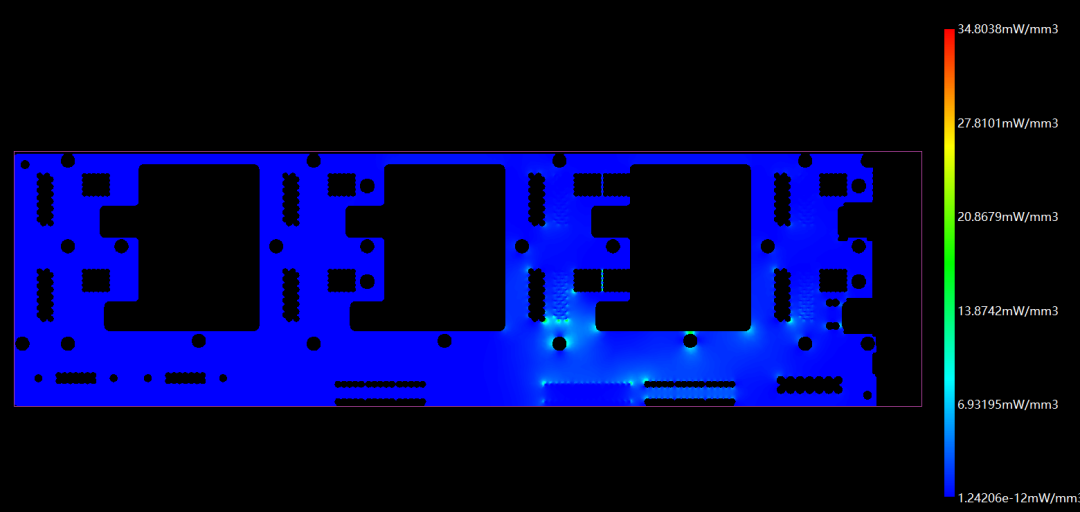

功耗分析

功耗沒(méi)有過(guò)大的情況,功耗密度云圖分布未出現(xiàn)異常,功耗評(píng)估合理。

功耗結(jié)果表格

功耗密度分布云圖1

功耗密度分布云圖2

仿真結(jié)論

此背板在載流240A的情況下,壓降、功耗、電流熱點(diǎn)等仿真數(shù)據(jù)合理,在評(píng)估裕量?jī)?nèi),2D結(jié)果分布云圖沒(méi)有出現(xiàn)異常,故認(rèn)為載流240A的方案可行。

適配行業(yè)

PhySimET是由芯瑞微(上海)電子科技有限公司,基于自主知識(shí)產(chǎn)權(quán)技術(shù)開發(fā)的電熱協(xié)同仿真工具。

PhySimET充分考慮電與熱之間的相互影響,使用高精度網(wǎng)格剖分、高效精確的有限元(FEM)算法,實(shí)現(xiàn)對(duì)芯片級(jí)、板級(jí)等的電熱協(xié)同分析。PhysimET適用于多個(gè)行業(yè),如半導(dǎo)體、計(jì)算機(jī)、汽車、通信網(wǎng)絡(luò)

數(shù)據(jù)中心、交換機(jī)、服務(wù)器等行業(yè),幫助優(yōu)化其電子產(chǎn)品,縮短產(chǎn)品設(shè)計(jì)周期,提升產(chǎn)品競(jìng)爭(zhēng)力。

本次案例為PhySimET在通信、基站硬件行業(yè)中的應(yīng)用,使用戶在電子產(chǎn)品實(shí)體化前進(jìn)行有效仿真,規(guī)避潛在設(shè)計(jì)風(fēng)險(xiǎn)。

場(chǎng)景描述

基站電源的設(shè)計(jì)對(duì)整個(gè)電路板至關(guān)重要,將直接影響電路的功能性和穩(wěn)定性,若設(shè)計(jì)載流過(guò)大,將會(huì)引起一系列的直流問(wèn)題,嚴(yán)重情況下可能會(huì)造成設(shè)計(jì)電路因過(guò)熱而燒毀(焦耳熱效應(yīng)),若載流能力設(shè)計(jì)偏小,將造成設(shè)計(jì)閾值的冗余和硬件成本的浪費(fèi)。所以對(duì)該產(chǎn)品進(jìn)行直流優(yōu)化在設(shè)計(jì)方面至關(guān)重要。

案例簡(jiǎn)介

本案例用戶希望通過(guò)PhySimET來(lái)確認(rèn)此設(shè)計(jì)的最大載流能力。未優(yōu)化的原始設(shè)計(jì)載流為120A,電源背板最大可承載溫度為100℃,計(jì)劃通過(guò)仿真手段探索載流能力的上限,從而保證電源背板在溫度不超限值情況下,實(shí)現(xiàn)最大的設(shè)計(jì)載流能力。

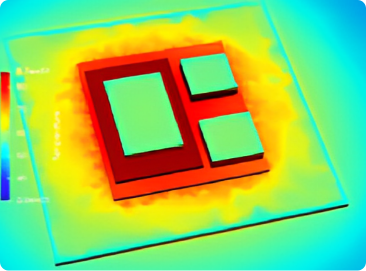

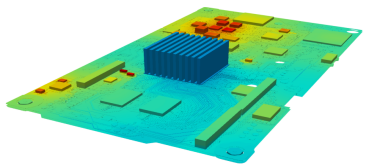

仿真效果

通過(guò)PhySimET仿真發(fā)現(xiàn),該電源背板的最大載流能力在達(dá)到180A后依然有較高的直流和熱的優(yōu)秀表現(xiàn),于是將背板載流設(shè)計(jì)優(yōu)化成180A,大幅提升了電源背板的載流性能,設(shè)計(jì)閾值大幅提升。

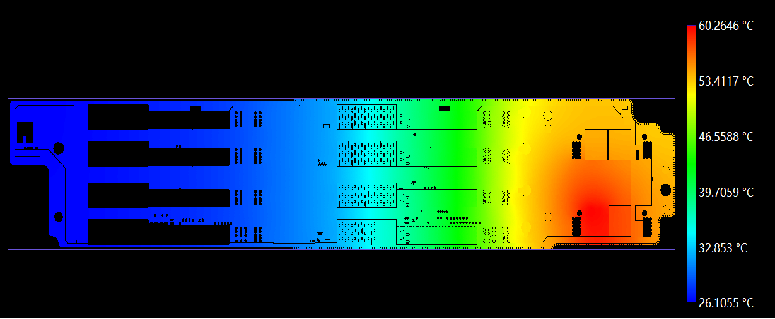

優(yōu)化前

用戶的原始設(shè)計(jì)載流為120A。

優(yōu)化后

通過(guò)PhySimET優(yōu)化后,載流能力變?yōu)?80A。

PhySimET在此案中的價(jià)值點(diǎn)

其主要的價(jià)值點(diǎn)在于,通過(guò)電源完整性仿真分析代替?zhèn)鹘y(tǒng)的實(shí)驗(yàn)手段,實(shí)現(xiàn)對(duì)原始設(shè)計(jì)電流的快速優(yōu)化迭代,尋找設(shè)計(jì)性能的最優(yōu)(溫度不超限值),將供電性能在可靠性和散熱要求下達(dá)到極致水平,并且PhySimET仿真耗時(shí)較短,精度準(zhǔn)確(與商用電熱仿真軟件相比,最高溫度相差2℃以內(nèi))。

1、適配行業(yè):

通信、基站硬件行業(yè)。

2、場(chǎng)景描述:

客戶一站式服務(wù)需求,利用FPGA芯片/RSICV芯片以及外圍阻容等器件開展SiP定制設(shè)計(jì)。

3、案例介紹:

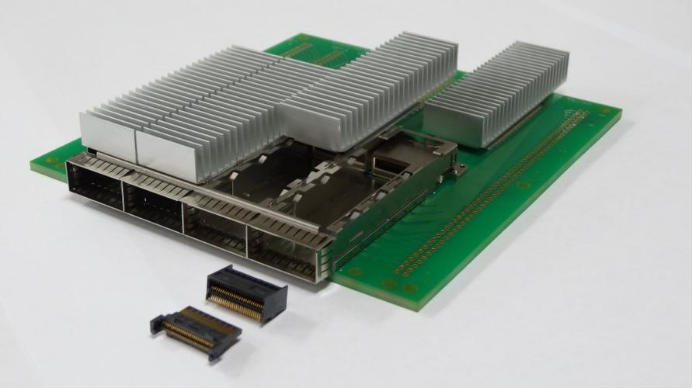

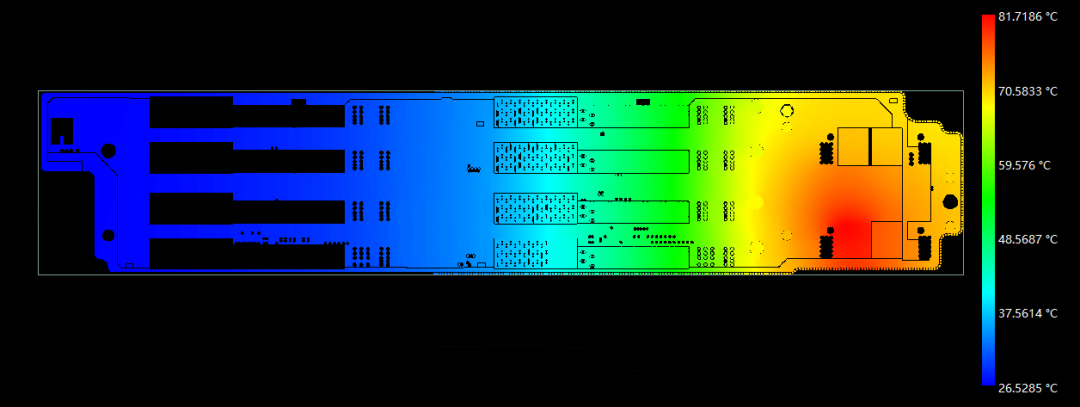

該方案使用FC+WB混合組裝方法,在ABF(Adaptive Beam Forming)基板頂部將FPGA、RISCV芯片和Flash組成微系統(tǒng)并通過(guò)焊盤進(jìn)行互聯(lián)。ABF基板底部利用BGA焊球與PCB實(shí)現(xiàn)導(dǎo)通。再在整個(gè)系統(tǒng)外部增加金屬蓋實(shí)現(xiàn)散熱,金屬蓋與ABF基板采用導(dǎo)熱硅脂粘接完成。

在基板設(shè)計(jì)完成之后,進(jìn)行對(duì)設(shè)計(jì)是否正確、系統(tǒng)性能、產(chǎn)品質(zhì)量和可靠性等進(jìn)行評(píng)估。這時(shí),需要進(jìn)行SiP仿真分析:熱(Thermal Simulation)、直流(DCSimulation)、信號(hào)完整性(Signal Integrity Simulation)、電源噪聲仿真(Power Delivery Network Simulatioon)。

系統(tǒng)封裝設(shè)計(jì)完成后,進(jìn)行開發(fā)板設(shè)計(jì)。該開發(fā)板提供Socket接口、電源輸入、Debug接口、全局復(fù)位電路、時(shí)鐘系統(tǒng)、存儲(chǔ)接口(DDR、mirco SD)、以太網(wǎng)接口、USB接口、音頻接口、FMC插座等。

4、案例效果:

實(shí)現(xiàn)高集成度、小體積:尺寸不超過(guò)40X40mm,基板厚度不超過(guò)1mm,層數(shù)不超過(guò)10層。

多維度應(yīng)用:可實(shí)現(xiàn)多類別應(yīng)用,如存儲(chǔ)功能(DDR、eMMC),音頻功能、千兆以太網(wǎng)、USB數(shù)據(jù)傳輸?shù)取?/p>

該系統(tǒng)主頻不低于800MHz,運(yùn)算能力不低于2.0DMIPS/MHz,浮點(diǎn)運(yùn)算能力不低于4MFLOPS/MHz,F(xiàn)PGA容量不低于326,000 Logic Cells。

5、本公司在方案中的優(yōu)勢(shì):

本公司根據(jù)客戶需求,進(jìn)行SiP方案一站式設(shè)計(jì)服務(wù),縮短產(chǎn)品開發(fā)周期,減少客戶端開發(fā)應(yīng)用成本:原理圖設(shè)計(jì)、封裝設(shè)計(jì)、自主開發(fā)軟件進(jìn)行仿真驗(yàn)證(熱仿真、直流仿真、信號(hào)完整性仿真、電源噪聲仿真等)、基板封裝加工生產(chǎn)測(cè)試、開發(fā)板設(shè)計(jì)組裝和測(cè)試。

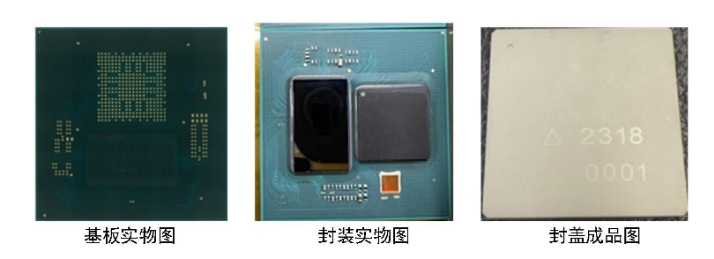

1、服務(wù)器載板(大尺寸PCB)

| 尺寸 | 64*42.5cm |

層數(shù) | 14L |

| 銅厚 | L6~L9:1oz;其余層0.5oz |

| 總厚度 | 2.97mm |

| 最小孔徑 | 0.2mm |

| 表面處理 | 沉金 |

| 工藝難點(diǎn) | 阻抗要求種類數(shù)量繁多,大尺寸 |

| 交期 | PCB制板周期:22天 |

實(shí)物展示

2、剛撓板

| 尺寸 | 14.076*5.088 cm |

| 層數(shù) | 12L L3~L10為軟板層 |

| 銅厚 | 0.5oz |

| 總厚度 | 2.2mm |

| 最小孔徑 | 1 mil |

| 表面處理 | 沉金 |

| 工藝難點(diǎn) | 軟板到孔的距離≥1.0mm;軟板層有阻抗需求 |

| 交期 | PCB制板周期:20天 |

3、補(bǔ)強(qiáng)板

| 尺寸 | 51.9*132.95mm |

| 層數(shù) | 8L(L3-L6為軟板層) |

| 銅厚 | 內(nèi)層 0.5oz 外層1oz |

| 總厚度 | 1.6mm,補(bǔ)強(qiáng)區(qū)域:10.2mm |

| 最小孔徑 | 0.2mm |

| 表面處理 | 沉金 |

| 工藝難點(diǎn) | 在8L軟硬結(jié)合板的基礎(chǔ)上增加補(bǔ)強(qiáng),厚度由1.6mm→10.2mm, 厚度工差±0.4mm |

| 交期 | PCB+PCBA威品制造周期25天 |

| 尺寸 | 6.82*6.82mm |

| 層數(shù) | 4L |

| 銅厚 | 1 oz |

| 總厚度 | 1.5mm |

| 表面處理 | 鎳鈀金 |

| 工藝難點(diǎn) | 4LPCB臺(tái)階板,兩階臺(tái)階,成品厚度:1.5mm,克服焊盤溢膠問(wèn)題 |

| 交期 | PCB制板時(shí)間:15天 |

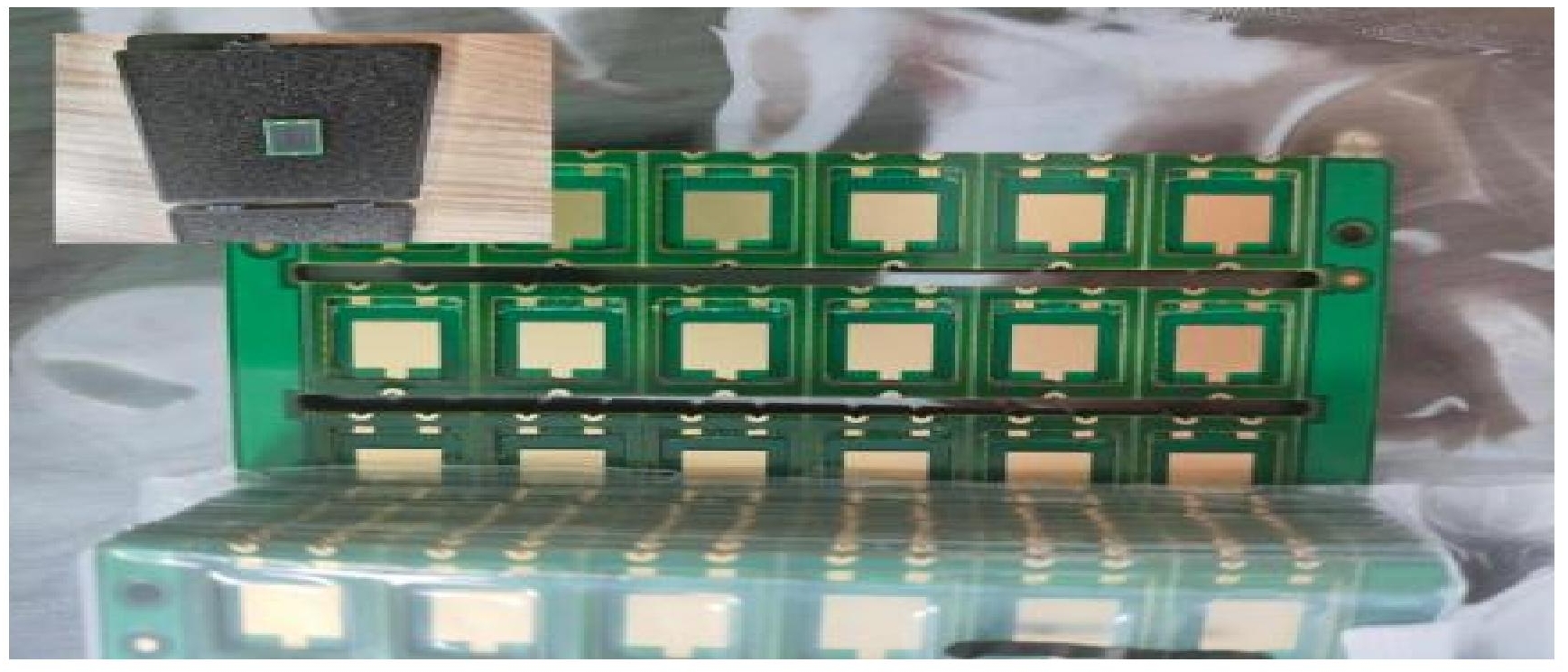

4、臺(tái)階板

實(shí)物展示

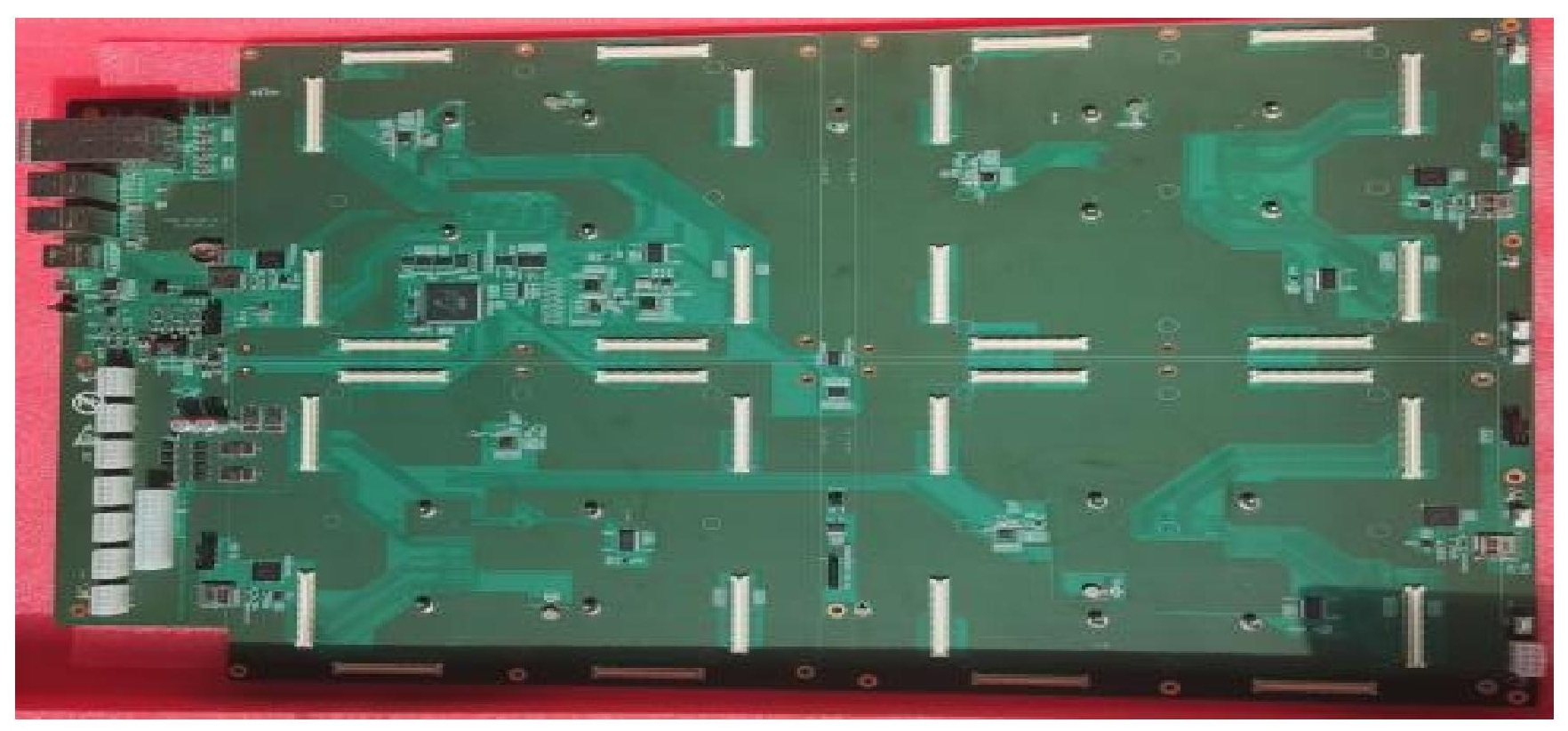

5、COB打線板

| 尺寸 | 18.5*6.2cm |

| 層數(shù) | 16L |

| 銅厚 | 1 oz |

| 總厚度 | 2mm |

| 表面處理 | 鎳鈀金 |

| 工藝難點(diǎn) | 電氣孔密集,不同網(wǎng)絡(luò)孔邊與孔邊之間最小距離為11mil, |

| 交期 | PCB制板時(shí)間:15天,貼裝+打線:9天 |

實(shí)物展示

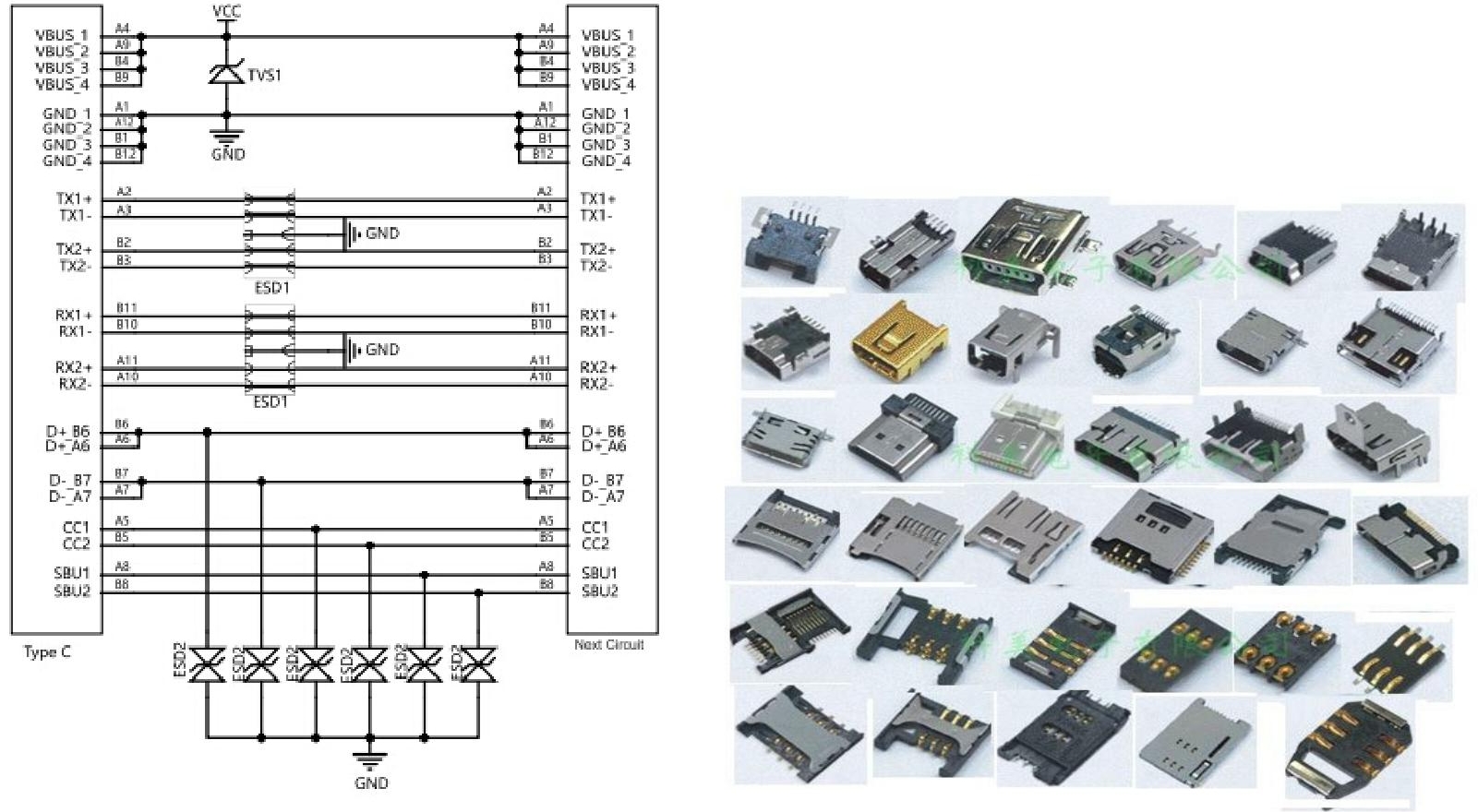

底部連接器

1、適配行業(yè):

底部連接器設(shè)計(jì)廣泛應(yīng)用在移動(dòng)消費(fèi)類產(chǎn)品上,目前市場(chǎng)上應(yīng)用產(chǎn)品主要為移動(dòng)電話、PDA、DSC(數(shù)碼相機(jī))以及MP3等便攜產(chǎn)品。

2、場(chǎng)景描述:

由于是直流回路,可選用普通電容器件。此端口可能會(huì)受到高能量的沖擊,可以選用集成TVS或分立的器件。

3、案例介紹: